在當(dāng)今大數(shù)據(jù)時(shí)代,數(shù)據(jù)中心作為數(shù)據(jù)處理和存儲(chǔ)服務(wù)的核心基礎(chǔ)設(shè)施,面臨著日益增長(zhǎng)的計(jì)算需求與成本控制的雙重挑戰(zhàn)。尤其在圖像處理領(lǐng)域,傳統(tǒng)的CPU解決方案往往無(wú)法兼顧高性能與低能耗,導(dǎo)致用戶體驗(yàn)與服務(wù)成本難以取得理想平衡。FPGA(現(xiàn)場(chǎng)可編程門陣列)與CPU的協(xié)同計(jì)算架構(gòu),正在為這一難題提供創(chuàng)新解決方案,推動(dòng)數(shù)據(jù)中心在圖像處理應(yīng)用中實(shí)現(xiàn)效率與成本的新平衡。

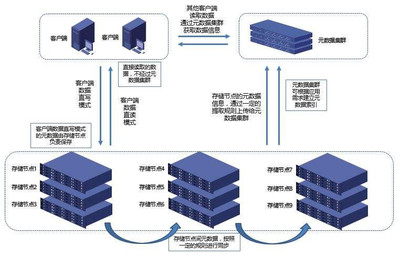

FPGA+CPU的異構(gòu)計(jì)算模式顯著提升了數(shù)據(jù)中心的圖像處理性能。圖像處理任務(wù)通常涉及大量并行計(jì)算,例如圖像識(shí)別、特征提取和實(shí)時(shí)視頻分析等。FPGA以其高度并行的硬件架構(gòu)和可定制邏輯單元,能夠高效執(zhí)行這些計(jì)算密集型操作,而CPU則負(fù)責(zé)處理控制流和復(fù)雜邏輯任務(wù)。這種分工協(xié)作不僅加速了圖像數(shù)據(jù)的處理速度,還減少了CPU的負(fù)載,從而優(yōu)化了整體系統(tǒng)響應(yīng)時(shí)間,為用戶帶來(lái)更流暢的應(yīng)用體驗(yàn)。

FPGA+CPU架構(gòu)在服務(wù)成本方面展現(xiàn)出顯著優(yōu)勢(shì)。傳統(tǒng)的純CPU方案在應(yīng)對(duì)高并發(fā)圖像處理時(shí),往往需要部署更多服務(wù)器,導(dǎo)致能源消耗和設(shè)備維護(hù)成本急劇上升。而FPGA具有低功耗和可重配置的特性,能夠在特定任務(wù)中實(shí)現(xiàn)更高的能效比。通過(guò)將部分計(jì)算任務(wù)卸載到FPGA,數(shù)據(jù)中心可以減少對(duì)昂貴CPU資源的依賴,降低電力開(kāi)銷和硬件投資,從而在保障服務(wù)質(zhì)量的同時(shí),有效控制運(yùn)營(yíng)成本。

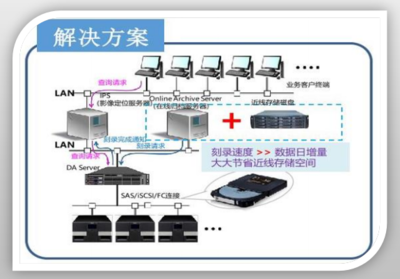

FPGA+CPU的靈活性為數(shù)據(jù)中心的圖像處理服務(wù)提供了更強(qiáng)的適應(yīng)性。隨著應(yīng)用場(chǎng)景的多樣化,如圖像增強(qiáng)、醫(yī)學(xué)影像分析和自動(dòng)駕駛視覺(jué)系統(tǒng)等,需求不斷變化。FPGA的可編程性允許數(shù)據(jù)中心根據(jù)具體應(yīng)用快速調(diào)整硬件邏輯,而無(wú)需更換整個(gè)系統(tǒng)架構(gòu)。這種動(dòng)態(tài)優(yōu)化能力不僅縮短了開(kāi)發(fā)周期,還提高了資源利用率,進(jìn)一步強(qiáng)化了服務(wù)成本效益。

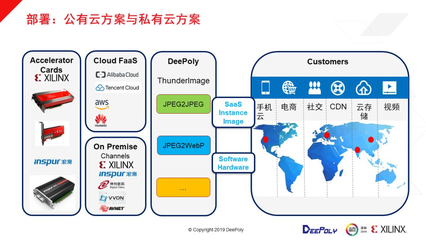

實(shí)現(xiàn)FPGA+CPU的協(xié)同并非沒(méi)有挑戰(zhàn)。例如,編程復(fù)雜性和系統(tǒng)集成難度可能增加初期部署成本。但通過(guò)標(biāo)準(zhǔn)化工具鏈和云服務(wù)提供商的支持,這些障礙正逐步被克服。許多領(lǐng)先的數(shù)據(jù)中心已開(kāi)始采用FPGA加速卡與CPU結(jié)合的方式,在圖像處理、機(jī)器學(xué)習(xí)推理等場(chǎng)景中取得顯著成果。

FPGA+CPU的異構(gòu)計(jì)算架構(gòu)為數(shù)據(jù)中心在圖像處理領(lǐng)域開(kāi)辟了一條新路徑。它不僅在數(shù)據(jù)處理速度上實(shí)現(xiàn)了突破,還通過(guò)優(yōu)化資源分配和降低能耗,在服務(wù)成本與用戶體驗(yàn)之間找到了可持續(xù)的平衡點(diǎn)。未來(lái),隨著技術(shù)的不斷成熟,F(xiàn)PGA+CPU有望在更多數(shù)據(jù)處理和存儲(chǔ)服務(wù)中發(fā)揮關(guān)鍵作用,推動(dòng)數(shù)據(jù)中心向更高效、更經(jīng)濟(jì)的方向演進(jìn)。